1.C言語によるハードウェア設計の概要

(1)C言語によるハードウェア設計の概要

(2)HLSの概要

2.ハードウェア設計のポイント

(1)C言語とのコーディングの違い

(2)作成されたハードウェアへの評価

3.HLS入門

(1)HLSの基本構文

(2)ハードウェア部分とテストベンチ部分について

(3)HLSの設計フロー

(4)Exampleプロジェクトの実行

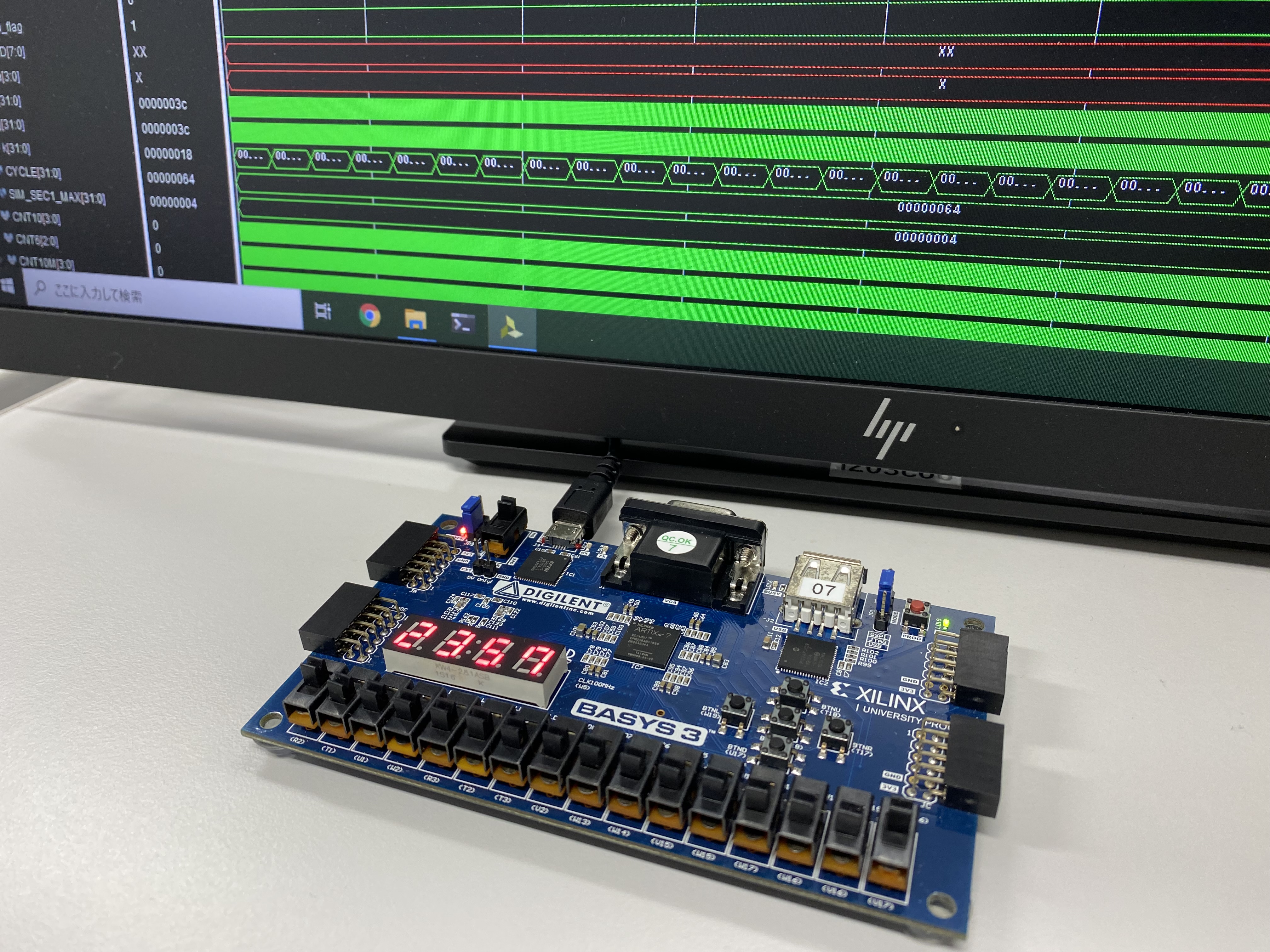

4.FPGA上での動作

(1)ハード単体での動作

(2)アルゴリズムのハードウェア化

(3)AXIインターフェース

(4)ソフトCPUからのアクセス

5.まとめ

≪担当予定講師≫

設計アナリスト 鳥海 佳孝

(日本電気㈱、エクセレント・デザイン㈱を経て独立。LSI/FPGA、組込みLinuxの設計開発・コンサルティングの業務を展開、各種技術セミナーの講師を務める)

コース番号 T0211 C言語によるハードウェア設計技術(Vivado HLS 編)<FPGA開発シリーズ5>

訓練日程

10/30(水)~11/1(金)

実施時間帯

10:00~16:45(昼休憩45分)

総訓練時間

18時間

受講料

29,500円

定員

14名

対象者

~C言語の資産をハードウェア設計に活かしたい!~

C言語によるLSI(FPGA)設計業務を担当する方

≪訓練内容の概要≫

C言語からHDL(Hardware Description Language)に変換するツールを無償で使用する事ができるようになりました。これによってC言語を活用したハードウェア設計の環境がより身近なものとなりました。そこで本セミナーでは、VitisとFPGAの評価ボードを用いた実習を通して、C言語を活用した回路設計手法を習得します。

≪前提知識≫

T0171「HDLによるLSI開発技術(Verilog-HDL編)」修了程度の知識およびC言語の基礎知識

C言語によるLSI(FPGA)設計業務を担当する方

≪訓練内容の概要≫

C言語からHDL(Hardware Description Language)に変換するツールを無償で使用する事ができるようになりました。これによってC言語を活用したハードウェア設計の環境がより身近なものとなりました。そこで本セミナーでは、VitisとFPGAの評価ボードを用いた実習を通して、C言語を活用した回路設計手法を習得します。

≪前提知識≫

T0171「HDLによるLSI開発技術(Verilog-HDL編)」修了程度の知識およびC言語の基礎知識

訓練内容

使用機器・教材

FPGA評価ボード(XILINX製FPGA) ソフトウェア:FPGA開発ツール(Vivado、Vitis)

持参品・服装

実施場所

高度ポリテクセンター

備考