1.FPGA開発フロー

(1)トップダウン設計の概要

(2)記述レベル(ビヘイビア記述、RTL記述、ゲート記述)の概念

2.VHDL詳細

(1)VHDL概要

(2)VHDLの文法

(3)簡単な記述例(RTL記述とテストベンチ記述)

3.実習:その1

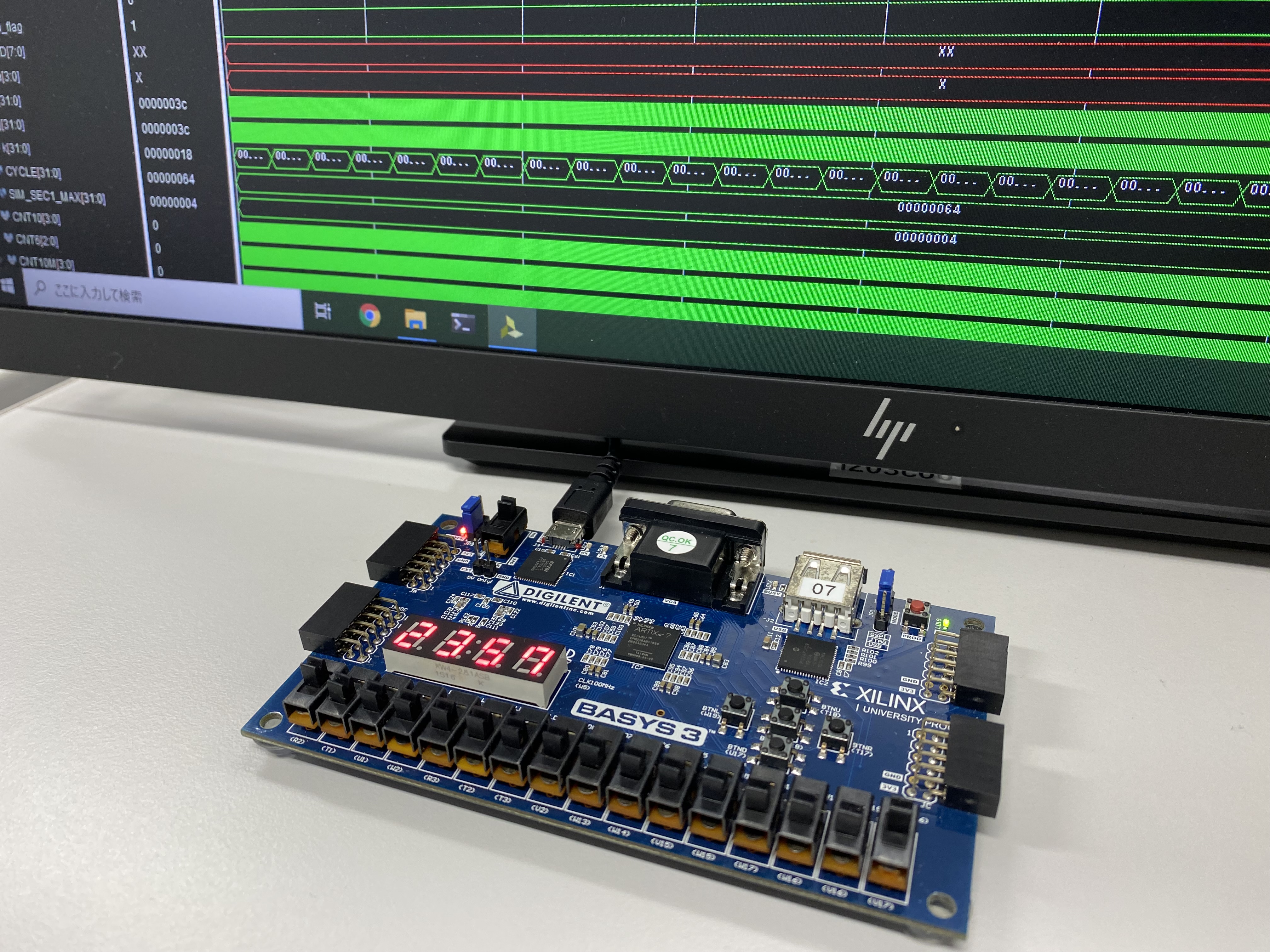

(1)論理シミュレータの使い方

(2)カウンタ、デコーダの作成と論理シミュレーション

4.テストベンチの考え方

(1)テストベンチ作成上の注意点

(2)テスト項目の洗い出し

5.VHDLの代入文

(1)signal(<=)

(2)variable(:=)

(3)デルタ・ディレイ

(4)動作の違いの確認実習

6.論理合成とRTL記述

(1)論理合成ツール概要

(2)スタティックな遅延解析と単相同期設計

(3)順序回路と組み合わせ回路のRTL記述例

7.実習:その2

(1)論理合成ツールの使い方

(2)順序回路、組合せ回路を使った論理合成の試行

8.RTL記述の注意点

(1)RTL記述とゲート記述のシミュレーションの違い

(2)順序回路と組合せ回路を意識した記述の仕方

9.総合演習

(1)ディジタル時計

≪担当予定講師≫

設計アナリスト 鳥海 佳孝

(日本電気㈱、エクセレント・デザイン㈱を経て独立。LSI/FPGA、組込みLinuxの設計開発・コンサルティングの業務を展開、各種技術セミナーの講師を務める)

コース番号 T0181 HDLによるLSI開発技術(VHDL編)<FPGA開発シリーズ1B>

訓練日程

7/17(水)~7/19(金)

実施時間帯

10:00~16:45(昼休憩45分)

総訓練時間

18時間

受講料

29,500円

定員

14名

対象者

~組合せ回路と順序回路、意識して書き分けていますか?~

VHDLによるFPGA/PLD開発担当者

≪訓練内容の概要≫

FPGAの評価ボードを用いた実習を通じて、VHDLによるFPGA開発技術を習得できます。FPGAの設計フロー及び文法事項と設計手順を理解し、評価ボード上にデジタル回路を設計することにより、実務レベルで役立つVHDL記述によるハードウェア設計手法を習得できます。

≪前提知識≫

同期カウンタがわかる程度のデジタル回路の知識

VHDLによるFPGA/PLD開発担当者

≪訓練内容の概要≫

FPGAの評価ボードを用いた実習を通じて、VHDLによるFPGA開発技術を習得できます。FPGAの設計フロー及び文法事項と設計手順を理解し、評価ボード上にデジタル回路を設計することにより、実務レベルで役立つVHDL記述によるハードウェア設計手法を習得できます。

≪前提知識≫

同期カウンタがわかる程度のデジタル回路の知識

訓練内容

使用機器・教材

ハードウェア:FPGA評価ボード(XILINX製FPGA) ソフトウェア:FPGA開発ツール(Vivado)

持参品・服装

実施場所

高度ポリテクセンター

備考

関連コース

- T0191 HDLによる実用回路設計手法<FPGA開発シリーズ4>

- T0201 HDLテストベンチ記述手法<FPGA開発シリーズ2>

- T0501 HDLによる入出力コントローラの設計と実装技術<FPGA開発シリーズ3>

- T0211 C言語によるハードウェア設計技術(Vivado HLS 編)<FPGA開発シリーズ5>

受講者の声

- これまでVHDLの記述とハードウェアが自分の中でうまく結びつけて考えられていなかったため、今回のセミナーでその辺りの考え方を身につけられて良かった。