Renewコースのご紹介

何となく動作する回路。記述を見直したらダイサイズを小さくできるかもしれません。

HDLによる回路設計手法(実用回路編)

【FPGA開発シリーズ3】

HDLによるFPGA/PLD開発担当者

【開催予定日(コース番号・日程)】

T0191 2016年11月16日(水)~11月18日(金)【受講料】

28,000円【定員】

12名

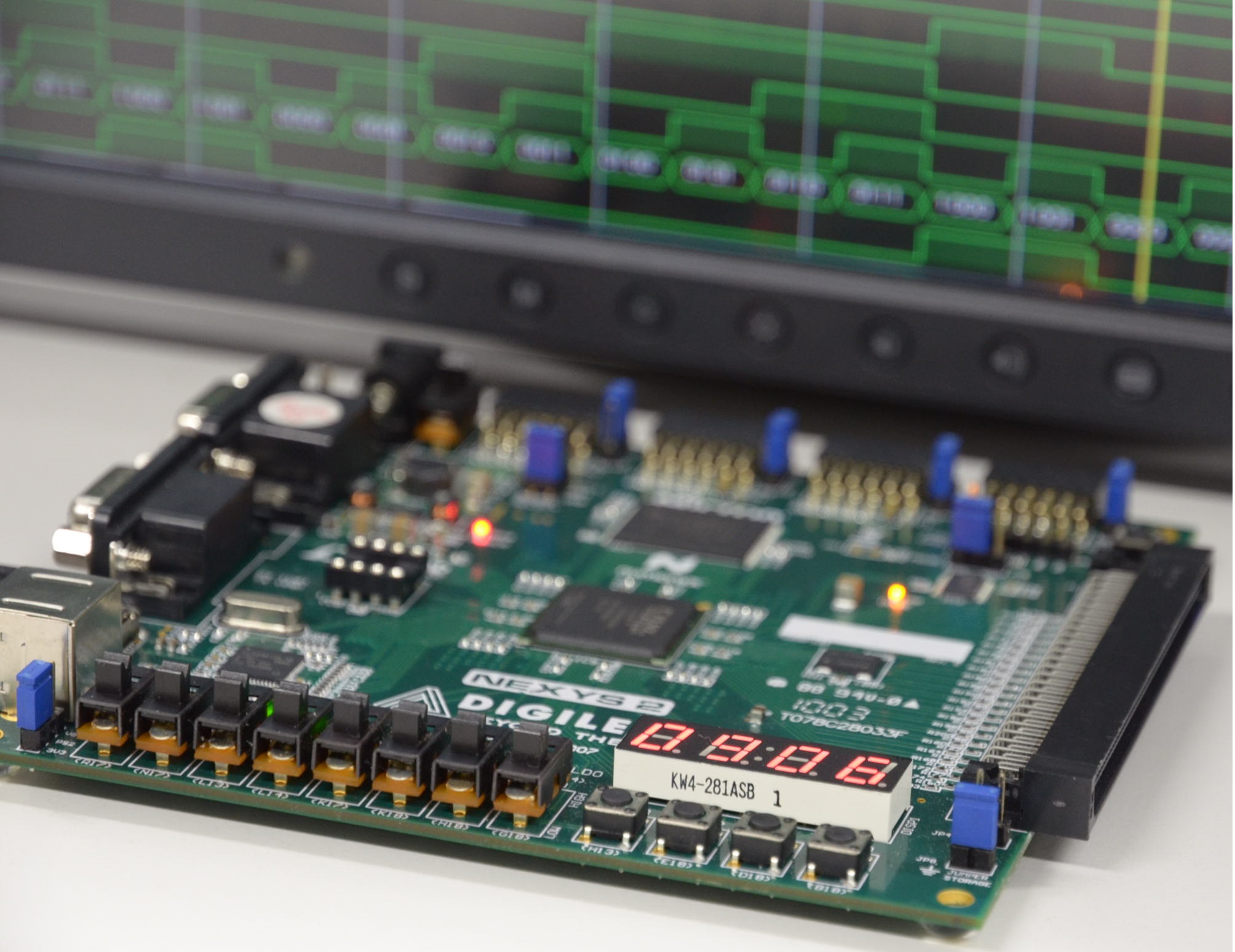

ターゲットボードに実装して動作させます

1.コースの概要

「VHDL/Verilog-HDLによるLSI(FPGA)開発技術」の続編コースです。基本的なHDL記述ができる方を対象に、FPGAの開発に必要な様々なエッセンスを含む演習を通して、より実践的な設計手法を習得することができます。また、FPGAの設計でお悩みの方のために、設計カウンセリングの場を設け、問題解決の糸口にして頂きます。

2.使用機器等

3.担当予定講師

4.ご受講に際して

5.関連コース

6.その他

FPGA評価ボード、FPGA開発ツール、Verilog・VHDLシミュレータ

3.担当予定講師

設計アナリスト 鳥海 佳孝(日本電気㈱、エクセレント・デザイン㈱を経て独立。LSI/FPGA、組込みLinuxの設計開発・コンサルティングの業務を展開、各種技術セミナーの講師を務める)

4.ご受講に際して

1日の開講時間は、10:00~16:45(昼休憩45分)の6時間 (計18時間) となります。

5.関連コース

T020

T050

T021

E023

6.その他

【前提知識】「VHDL/Verilog-HDLによるLSI(FPGA)開発技術」修了程度の知識

受講者の声

- 設計の基礎を再確認できたため、今までの設計の進め方を見直すきっかけになると感じた

- メタ・ステーブル等回路を意識せずに記述していた。また、再利用を考えると仕様や設計の部分でしっかり考えないといけないなと再認識できた。

- FFにするorしないの考え方が理解できた。シミュレーションがしやすい記述の説明が為になりました。

- やってはいけない記述の説明が詳しくてよかった。

7.カリキュラム概要※

| 教科項目 | 教科細目 | 時間 |

|---|---|---|

| 1.24時間時計仕様検討 | (1)機能検討

(2)ブロック図作成 (3)タイミング図作成 (4)仕様レビュー |

2.0H |

| 2.24時間時計詳細設計 | (1)単相同期設計

(2)キャリーの作り方 (3)論理シミュレーション・デバッグのテクニック (4)シーケンサの使い方 (5)メタ・ステーブル対策 (6)設計レビュー (7)LSI・FPGA設計カウンセリング ※実習中に適宜対応します |

14.0H |

| 3.まとめ | (1)仕様作成のポイント

(2)設計のポイント |

1.0H |

| 4.最近の設計手法のトレンド紹介 | (1)CベースによるFPGA設計概要 | 1.0H |

※お申し込み頂く際の目安です。詳細等のご質問は下のお問い合わせまでお願いします。

また、都合により予告無く内容が変更になる場合がございますので、予めご了承ください。