Renewコースのご紹介

組合せ回路と順序回路、意識して書き分けていますか?

Verilog-HDLによるLSI(FPGA)開発技術

【FPGA開発シリーズ1A】

Verilog-HDLによるFPGA開発担当者

【開催予定日(コース番号・日程)】

T0171 2016年06月08日(水)~06月10日(金)【受講料】

T0172 2016年09月07日(水)~09月09日(金)

26,500円【定員】

12名

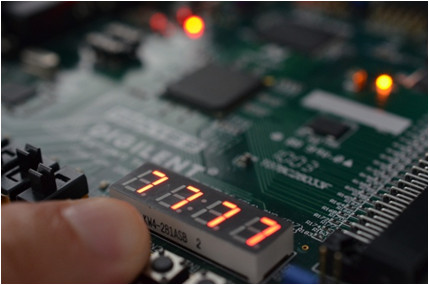

ターゲットボードに実装して動作させます

1.コースの概要

FPGAの評価ボードを用いた実習を通じて、Verilog-HDLによるFPGA開発技術を習得できます。FPGAの設計フロー及び文法事項と設計手順を理解し、評価ボード上にデジタル回路を設計することにより、実務レベルですぐに役立つVerilog-HDL記述によるハードウェア設計手法を習得できます。

2.使用機器等

3.担当予定講師

4.ご受講に際して

5.関連コース

6.その他

ハードウェア:FPGA評価ボード ソフトウェア:FPGA開発ツール、Verilogシミュレータ

3.担当予定講師

設計アナリスト 鳥海 佳孝(日本電気㈱、エクセレント・デザイン㈱を経て独立。LSI/FPGA、組込みLinuxの設計開発・コンサルティングの業務を展開、各種技術セミナーの講師を務める)

4.ご受講に際して

1日の開講時間は、10:00~16:45(昼休憩45分)の6時間 (計18時間) となります。

5.関連コース

T019

T050

T020

T021

6.その他

【前提知識】同期カウンタがわかる程度のデジタル回路の知識

受講者の声

- FPGAを扱うのは初めてだったので、今までになかった知識を得られた。

- 今までVerilog-HDLは読むことすらできなかったが、自分で作成することができるようになった。

- ツールの使い方が実用の壁になっていたので、一緒に学習できたのはありがたかった。

- 演習、課題が多くあったので、だんだんと身に付けることができました。

7.カリキュラム概要※

| 教科項目 | 教科細目 | 時間 |

|---|---|---|

| 1.FPGA開発フロー | (1)トップダウン設計の概要

(2)記述レベル(ビヘイビア・RTL・ゲート記述)の概念 |

1.0H |

| 2.Verilog-HDL詳細 | (1)Verilog-HDL概要

(2)Verilog-HDLの文法 (3)簡単な記述例(RTL記述とテストベンチ記述) |

3.0H |

| 3.実習:その1 | (1)論理シミュレータの使い方

(2)カウンタ、デコーダの作成と論理シミュレーション |

2.0H |

| 4.テストベンチの考え方 | (1)テストベンチ作成上の注意点

(2)テスト項目の洗い出し |

1.0H |

| 5.Verilog-HDLの代入文 | (1)ブロッキング代入文(=)

(2)ノン・ブロッキング代入文(<=) (3)動作の違いの確認実習 |

1.0H |

| 6.論理合成とRTL記述 | (1)論理合成ツール概要

(2)スタティックな遅延解析と単相同期設計 (3)順序回路と組合せ回路のRTL記述例 |

2.0H |

| 7.実習:その2 | (1)論理合成ツールの使い方

(2)順序回路、組合せ回路を使った論理合成の試行 |

2.0H |

| 8.RTL記述の注意点 | (1)論理合成によるリソースシェアリング

(2)RTL記述とゲート記述のシミュレーションの違い (3)順序回路と組み合わせ回路を意識した記述の仕方 |

2.0H |

| 9.総合演習 | (1)10進アップダウンカウンタ

(2)スロットマシン |

4.0H |

※お申し込み頂く際の目安です。詳細等のご質問は下のお問い合わせまでお願いします。

また、都合により予告無く内容が変更になる場合がございますので、予めご了承ください。