1.24時間時計仕様検討

(1)機能検討

(2)ブロック図作成

(3)タイミング図作成

2.24時間時計詳細設計

(1)単相同期設計

(2)キャリーの作り方

(3)論理シミュレーション・デバッグのテクニック

(4)シーケンサの使い方

(5)メタ・ステーブル対策

3.まとめ

(1)設計のポイント

≪担当予定講師≫

設計アナリスト 鳥海 佳孝(日本電気㈱、エクセレント・デザイン㈱を経て独立。LSI/FPGA、組込みLinuxの設計開発・コンサルティングの業務を展開、各種技術セミナーの講師を務める)

コース番号 T0191 HDLによる実用回路設計手法<FPGA開発シリーズ4>

訓練日程

9/24(水)~9/26(金)

実施時間帯

10:00~16:45

(昼休憩45分)

総訓練時間

18時間

受講料

29,500円

定員

14名

対象者

~何となく動作する回路。記述を見直したらダイサイズを小さくできるかもしれません~

HDLによるFPGA/PLD開発担当者

≪訓練内容の概要≫

HDLによるLSI開発技術」の続編コースです。基本的なHDL記述ができる方を対象に、FPGAの開発に必要な様々なエッセンスを含む演習(ディジタル時計(時計、アラーム、タイマー、ストップウォッチ)の製作)を通して、より実践的な設計手法を習得することができます。

≪前提知識≫

T0171またはT0181「HDLによるLSI開発技術」修了程度の知識

HDLによるFPGA/PLD開発担当者

≪訓練内容の概要≫

HDLによるLSI開発技術」の続編コースです。基本的なHDL記述ができる方を対象に、FPGAの開発に必要な様々なエッセンスを含む演習(ディジタル時計(時計、アラーム、タイマー、ストップウォッチ)の製作)を通して、より実践的な設計手法を習得することができます。

≪前提知識≫

T0171またはT0181「HDLによるLSI開発技術」修了程度の知識

訓練内容

使用機器・教材

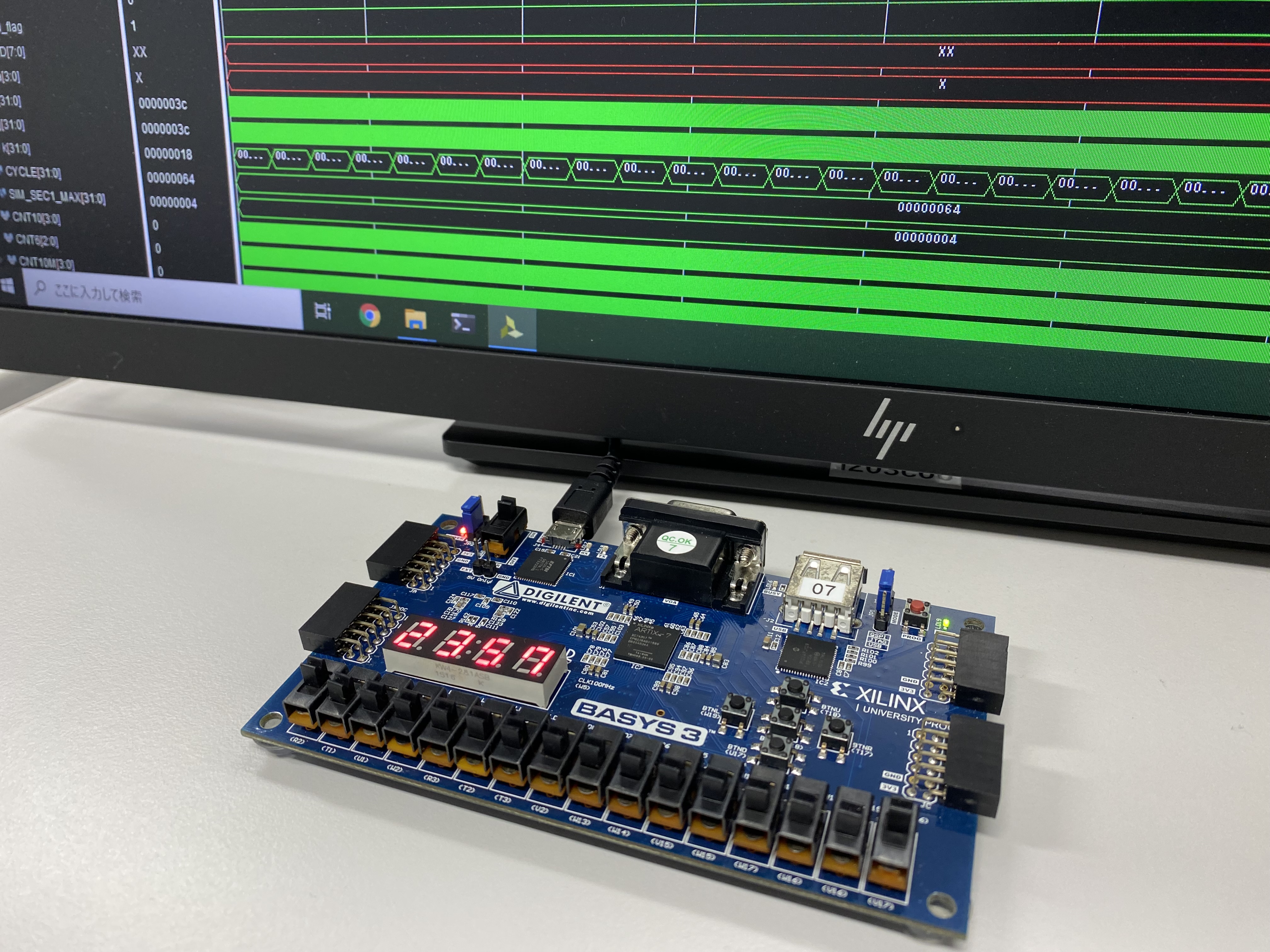

FPGA評価ボード(XILINX製FPGA) ソフトウェア:FPGA開発ツール(Vivado)

持参品・服装

実施場所

高度ポリテクセンター

備考

以下、関連コースです。

- T0171 HDLによるLSI開発技術(Verilog-HDL編)<FPGA開発シリーズ1A>

- T0181 HDLによるLSI開発技術(VHDL編)<FPGA開発シリーズ1B>

- T0201 HDLテストベンチ記述手法<FPGA開発シリーズ2>

- T0501 HDLによる入出力コントローラの設計と実装技術<FPGA開発シリーズ3>

- T0211 C言語によるハードウェア設計技術(Vivado HLS 編)<FPGA開発シリーズ5>

受講者の声

- 実用的なシーケンサの設計方法を学ぶことができた。