Newコースのご紹介

ハードウエアで画像処理をするために必要な技術要素を明確にします

FPGAによる高速画像処理技術

【FPGA開発シリーズ7】

画像処理システム構築の高速化を目指している方

【開催予定日(コース番号・日程)】

T0591 2017年01月19日(木)〜01月20日(金)【受講料】

23,000円【定員】

12名

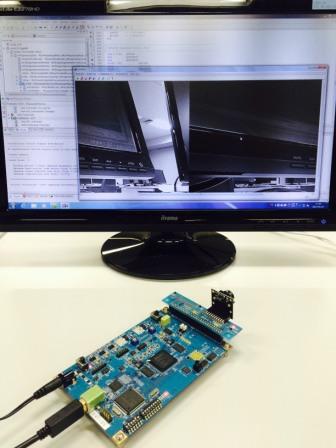

使用するFPGボード

1.コースの概要

近年、画像処理システムの高機能化と共に高速化の要求が高まっています。本コースでは、FPGAを用いたハードウエア技術による画像処理の高速化設計手法について学びます。具体的なフィルタ処理としてガウシアンフィルタのハードウエア実装を例にVerilog-HDLによる実践的な設計技法を習得できます。

2.使用機器等

3.担当予定講師

4.ご受講に際して

5.関連コース

6.その他

FPGA評価ボード、CMOSイメージセンサ、FPGA開発ツール

3.担当予定講師

ネットビジョン(株) 実際にCMOSイメージセンサ―のデジタル画像検証システム開発をされている経験豊富なエンジニアの方が講師です

4.ご受講に際して

1日の開講時間は、10:00〜16:45(昼休憩45分)の6時間 (計12時間) となります。

5.関連コース

T017

T019

T063

6.その他

【前提知識】「Verilog-HDLによるLSI(FPGA)開発技術」修了程度の知識

7.カリキュラム概要※

| 教科項目 | 教科細目 | 時間 |

|---|---|---|

| 1.コースの概要と開発環境構築 | (1)コース概要及び専門的能力の確認 (2)画像処理システムの概要と使用する画像処理ボード (3)開発ツールの概要と環境設定 | 1.0H |

| 2.CMOSイメージセンサの制御 | (1)周辺ハードウエアの構成 (2)イメージセンサ制御方法 (3)イメージセンサ制御用IP使用方法 | 2.0H |

| 3.画像処理のハードウエア化設計 | (1)ハードウエア化する画像処理のアルゴリズム (2)ガウシアンフィルターのハードウエア化検討 | 3.0H |

| 4.HDL設計 | (1)YUV信号取り出しモジュール回路設計 (2)ガウシアンフィルターのモジュール回路設計 (3)回路シミュレーションとFPGAへの実装 (4)設計した回路の動作確認および評価・改善 | 5.0H |

| 5.まとめ | (1)実習の全体的な講評及び確認・評価 | 1.0H |

※お申し込み頂く際の目安です。詳細等のご質問は下のお問い合わせまでお願いします。

また、都合により予告無く内容が変更になる場合がございますので、予めご了承ください。